半导体器件的ESD测试机器模型(MM)及静电敏感度分级

一、ESD机器模型

在半导体器件的制造、测试和电路板焊接组装的过程中,除了人体静电对器件可能造成潜在伤害,另一种重要的静电来源则是由于机器设备本身接地不良,在运行过程中产生静电积累。当机器或机械手臂碰触到IC时,静电经由IC的引脚(pin)放电。由于机器通常是金属材料,其等效电阻为0欧,其等效电容为200pF,故比较人体其放电的过程更短,在几纳秒到几十纳秒之内会有数安培的瞬间静电放电电流产生。

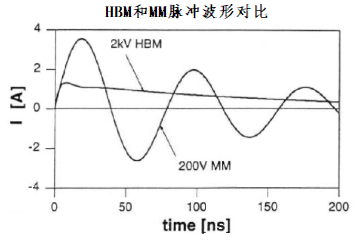

机器模型(MM) 2KV 和人体模型(HBM)200V放电脉冲波形比较如下图,虽然HBM的电压2KV比MM的电压200V高,但是200V MM的放电电流却比2KV HBV的放电电流大很多。放电电流波形有上下振荡(Ring)的情形,这是因为测试机台导线的杂散等效电感与电容互相耦合而引起的。因此机器模型的放电对IC的破坏力更大。

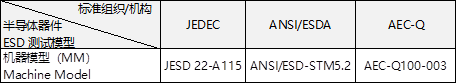

为了表征机器带静电并接触器件放电的电路特性,以及半导体器件的ESD敏感度,相关标准组织/机构制定了机器模型(Machine Model-MM)以规范MM模式下的ESD测试模型和等级标准。

以上相关的标准有所差异且被多次修订,但原理基本一致,本文以经典的JESD 22标准为参考进行说明。

二、 MM测试要求

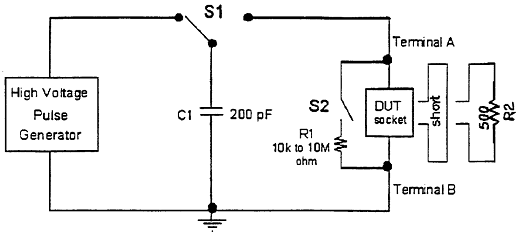

依据JESD22-A115-A (Oct, 1997),MM模型的测试等效电路如下图。等效机器电阻为0欧,C1 为等效机器电容。DUT(Device Under Test)为被测器件,放置在插座(socket)中。图中S1为充电和放电切换开关,S2用于释放DUT残留电荷,R2(500ohm负载)仅用于初始检测确认此模拟装置是否符合标准要求以及后续进行周期性的系统校调。标准建议短路(short)波形验证测试采用18-24AWG镀锡铜导线。

图1 ESD机器模型等效电路图

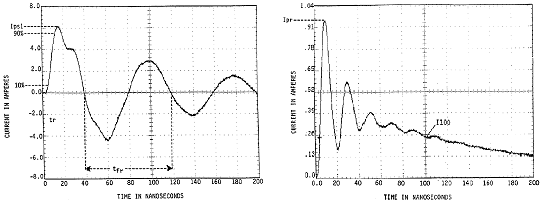

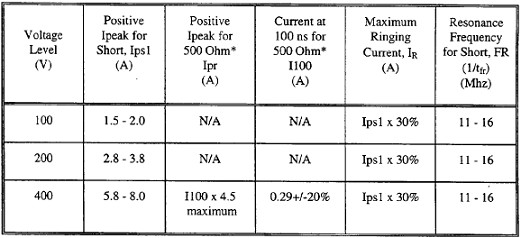

该等效模拟装置的测试电路要求符合以下脉冲波形指标要求:

图2 短路放电的电流波形@400V 图3 通过500ohm放电的电流波形@400V

在每次切换测试仪和更换测试插座(socket)/DUT板后一开始也都需要进行波形校验。如果任何一次波形不符合图1和表1(table 1)中 400V电压下的要求,则应停止测试,直到波形符合要求。

三、 器件MM等级测试

器件的ESD等级测试必须在已经完成所有制程和规格功能参数测试后的真实芯片上进行。在进行ESD测试之前,应对所有待进行ESD测试的样本器件完成室温下、或如果适用的更高温度条件下的直流参数和功能测试。被测试样本应满足器件手册的参数要求。

通常按照Table 1中所示的电压步长(Voltage Step)在每个电压等级(Voltage Level)上用3 个器件样本进行器件ESD失效阈值的表征。可以选择使用更精细的电压步长来获得更精确的失效阈值测量。ESD 测试应从Table 1中的最低步长开始。ESD测试应在室温条件下进行。

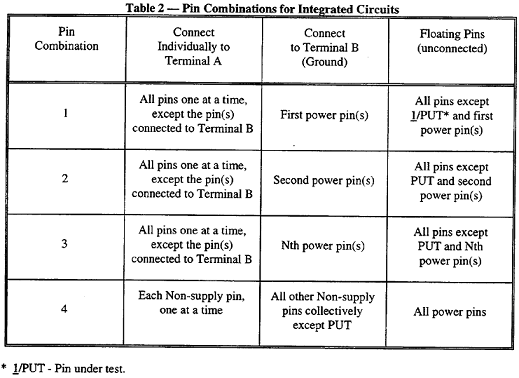

对于Table 2 中指定的所有引脚组合,3 个器件的每个样本都应以某一个电压等级(Voltage Level)在每个引脚上施加1个正向脉冲和1个负向脉冲应力,脉冲之间至少间隔 0.5 秒。对于Table 2 中指定的每一种引脚组合,使用3个器件中的一个单独样本是允许的。

当这3个样本全部都通过了该等级ESD测试后,仍然可以继续使用它们,施加下一个更高等级的脉冲电压,直到有器件发生失效。

引脚组合如Table 2 所示。引脚组合的实际数量取决于电源引脚组的数量。 通过金属导线(封装内部)直接连通的命名为“power”引脚(VCC1、VCC2、VSS1、VSS2、GND 等)可以连接在一起并作为一个引脚连接到Terminal B。 否则,必须应将每个”power”引脚视为单独的电源引脚。 不消耗电流的编程引脚(Programming Pins)应被视为 I/O 引脚(例如:存储器上的 Vpp 引脚)。 有源分立器件(FET、晶体管等)应使用所有可能的引脚对组合(一个引脚连接到Terminal A,另一个引脚连接到Terminal B )进行测试,而无论其引脚名称或功能。所有配置(configured)为“no connect”的引脚都应被验证确认是否在任何时候都是“无连接”且处于开路(悬空)状态。 标记为“no-connect”的引脚实际上如果是有连接的话,应作为非电源(non-supply)引脚进行测试。

如果在每个应力水平下都对不同的样本组进行了ESD 测试,则允许在所有样本组都经过 ESD 测试后执行 DC参数和功能性 ATE 测试。

在施加ESD脉冲后,器件不再能符合器件手册上的参数和功能测试规格要求,则该器件被定义为失效。如果要求进行多温度条件下的MM测试,应首先在最低温度下进行测试。

四、 器件HBM级别

所有样本都必须满足以上测试要求,直至达到特定的电压等级(Voltage Level),才能将该种器件归类为如下特定的静电敏感度分级(sensitivity classification)。

- CLASS A: 任何器件在施加200V或以下ESD脉冲后发生失效

- CLASS B: 任何器件在施加200V ESD脉冲后通过,但是施加400V ESD脉冲时发生失效

- CLASS C: 任何器件在施加400V ESD脉冲后全部通过

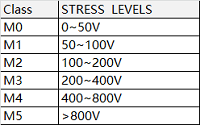

日本电子工业协会(EIAJ)在EIAJ-IC-121 mothod20标准中细分并扩展了JESD22-A115的MM分级。具体如下表:

芯片的第3种基本测试模型(CDM)及其静电敏感度分级将在后续文章中介绍。

--------------------------------------------------------------

该内容含有下载文件,请登录后再来下载!

该内容含有下载文件,请登录后再来下载!