半导体器件的ESD测试人体模型(HBM)及静电敏感度分级

ESD对半导体器件、以及电子产品和系统的可靠性设计和生产制造是一项很重要的影响因素。对于电子元器件,人体可能是产生静电损伤最主要的静电来源。

一、 HBM人体模型

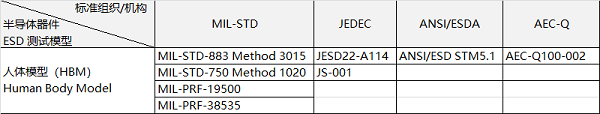

为了表征人体带静电并接触器件放电的电路特性,以及半导体器件的ESD敏感度,相关标准组织/机构制定了人体模型(Human Body Model-HBM)以规范HBM模式下的ESD测试模型和等级标准。

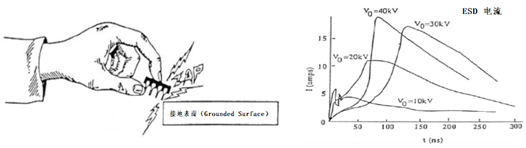

人体放电模型(HBM)的ESD是指因人体在走动摩擦或其它因素在人体上累积了静电,当此人碰触到IC时,人体上的静电便会经由IC的引脚(pin)而进入IC内,再经由IC放电到地。如左下图所示。

放电的过程会在短到几百纳秒(ns)的时间内产生数安培的瞬间放电电流,此电流会把IC内的组件给烧毁。 不同HBM静电电压相对产生的瞬间放电电流与时间的关系如右上图。对一般商用IC的2KV ESD放电电压而言,其瞬间放电电流的尖峰值大约是1.33 安培。

以上相关的标准有所差异且被多次修订,但原理基本一致,本文以经典的JESD 22标准为参考进行说明。

二、 HBM测试要求

依据JESD22-A114C (Jan, 2005),HBM模型的测试等效电路如下图。R1 为等效人体电阻,C1 为等效人体电容。DUT(Device Under Test)为被测器件,放置在插座(socket)中。图中S1为充电和放电切换开关,S2用于释放DUT残留电荷,R2(500ohm负载)仅用于初始检测确认此模拟装置是否符合标准要求以及后续进行周期性的系统校调。标准建议短路(short)波形验证测试采用18-24AWG镀锡铜导线。

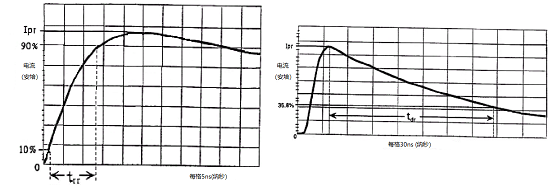

a) 脉冲上升时间tr b)脉冲衰减时间td

短路电流(Ips)波形

该等效模拟装置的测试电路要求在500ohm负载条件下应符合以下脉冲波形指标要求:

a) 脉冲上升时间trr b)脉冲衰减时间tdr

通过500oh电阻的电流(Ips)波形

Table 1-Waveform Specification

在短路条件下,脉冲从峰值(Ips)的10%上升到峰值的90%所需要的时间tr为脉冲上升时间,为2~10ns;脉冲从峰值下降到峰值的36.8%所需要的时间td为脉冲衰减时间,为150±20ns; 电流脉冲波形中第一个波峰与第一个波谷之间的差值IR为最大的振荡电流峰-峰值,应小于短路放电峰值电流Ips的15%。 500ohm负载条件下的脉冲波形指标要求如上表Table 1,不在此赘述。

三、 器件HBM等级测试

通常按照Table 1中所示的电压步长(Voltage Step)在每个电压等级(Voltage Level)上用3 个器件样本进行器件ESD失效阈值的表征。可以选择使用更精细的电压步长来获得更精确的失效阈值测量。ESD 测试应从Table 1中的最低步长开始。ESD测试应在室温条件下进行。

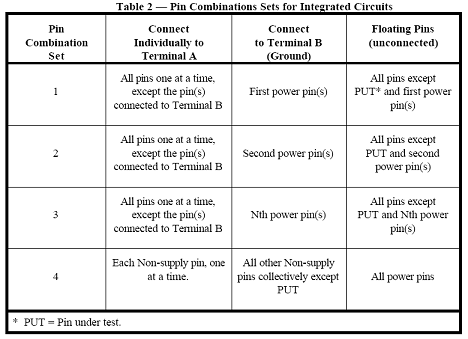

进行器件ESD等级测试时,3颗芯片的每个样本都按照Table 2给出的全部引脚组合以某一个电压等级(Voltage Level)对每个引脚施加1次正向和1次负向脉冲,正向和负向脉冲的间隔时间不小于100ms,考虑器件可能积累损伤,这个间隔时间可以加长。施加的脉冲电压通常从Table 1中最低的等级开始,但也可以从任何一个等级开始,当这3个样本全部都通过了该等级测试后,仍然可以继续使用它们,施加下一个更高等级的脉冲电压,直到有器件发生失效。但如果一开始用较高的初始脉冲电压导致器件失效,则应该换用全新的样本并从最低等级电压重新开始测试。

遵循Table 2中的引脚组合指引,参考其它标准,芯片ESD测试的引脚组合和连接方式有以下几种方式。

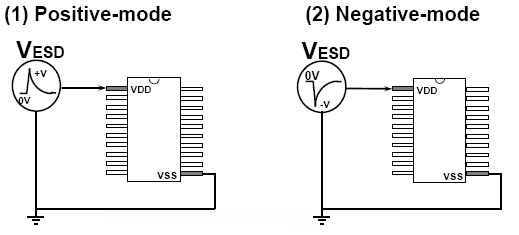

1)Pin对VDD/VSS测试

2)Pin对Pin测试

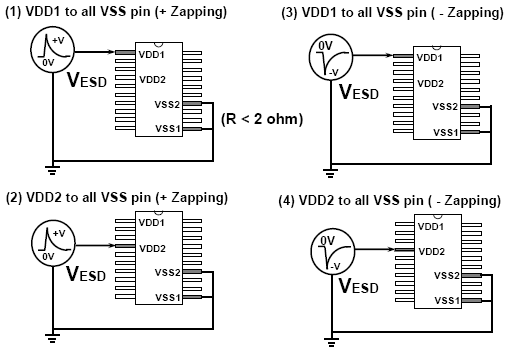

3)VDD对VSS测试

4)多VDD 对 多VSS测试

5)运放差分输入引脚间测试

在施加ESD脉冲后,器件不再能符合参数和功能测试规格要求,则被定义为失效。如果有特别要求进行多温度条件下的HBM测试,则应该从最低温度开始。

四、 器件HBM级别

为了给芯片进行静电敏感度分级(sensitivity classification),所有被测样品必须按照上述模型及测试方法进行测试标定。JESD22-A114将芯片的HBM等级划分如下:

CLASS 0: 施加250V或以下ESD脉冲,器件发生失效

CLASS 1A: 施加250V ESD脉冲时通过,但是施加500V ESD脉冲时器件发生失效

CLASS 1B: 施加500V ESD脉冲时通过,但是施加1000V ESD脉冲时器件发生失效

CLASS 1C: 施加1000V ESD脉冲时通过,但是施加2000V ESD脉冲时器件发生失效

CLASS 2: 施加2000V ESD脉冲时通过,但是施加4000V ESD脉冲时器件发生失效

CLASS 3A: 施加4000V ESD脉冲时通过,但是施加8000V ESD脉冲时器件发生失效

CLASS 1B: 施加8000V ESD脉冲时通过

五、待续

芯片的其它2种ESD基本测试模型(MM & CDM)及其静电敏感度分级将另文介绍。

--------------------------------------------------------------

*注:原创文章,版权所有。欢迎转载,请注明来源

该内容含有下载文件,请登录后再来下载!

该内容含有下载文件,请登录后再来下载!